# SINTER STATES

### **RELIABILITY:** The Fight Against Failure

### OUR LIBRARY IS ALWAYS OPEN

Registered members of my I-Connect007 have 24/7 access to our ever-growing library of eBooks, which now includes a wide range of topics from DFM to Complex PCBs.

Enrich your mind and expand your knowledge! Download these popular titles with just a click.

They're pretty awesome!

# Would you consider using low-temp solders?

In a recent survey, 75% said yes!

Source: I-Connect007 Research

This eBook will help you learn the advantages of lower temperature, including improving solder joints and lowering costs.

**Download Now**

#### JULY 2019 • FEATURED CONTENT

### **Reliability vs. Failure**

It should come as no surprise that solder and solder joints are often at the center of attention in electronics assembly when discussing failures and reliability. This issue includes articles and columns from industry experts as well as insightful technical papers on the cutting-edge of failure and reliability research.

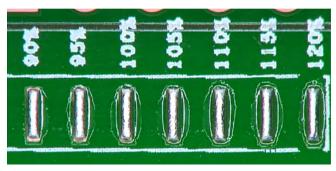

14 Optimizing Solder Paste Volume for Low-temperature Reflow of BGA Packages by Keith Sweatman

- 32 Size Matters: The Effects of Solder Powder Size on Solder Paste Performance by Tony Lentz

- 60 Low-temperature SMT Solder Evaluation by Howard "Rusty" Osgood, et al.

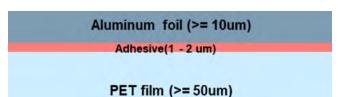

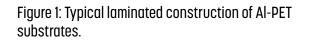

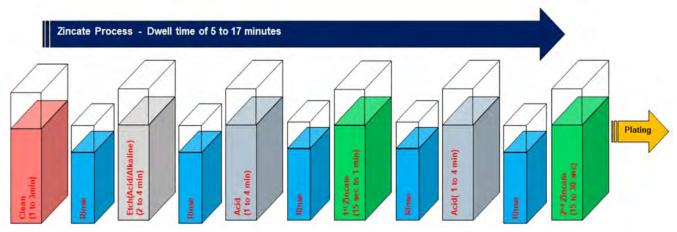

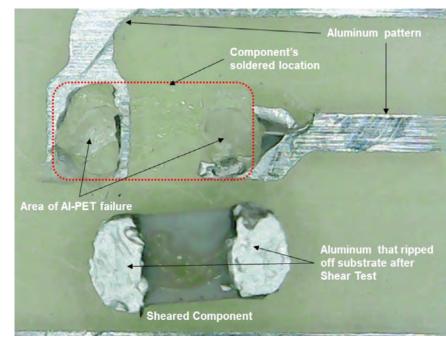

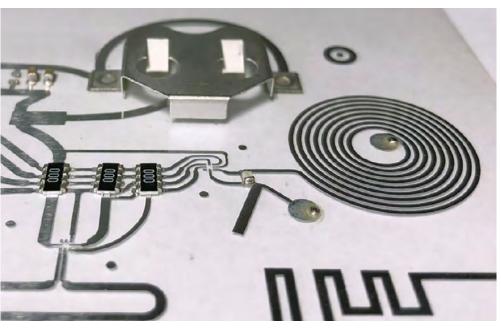

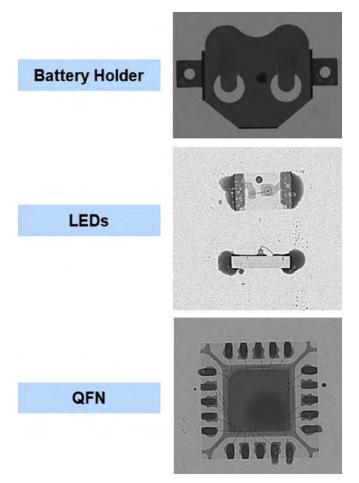

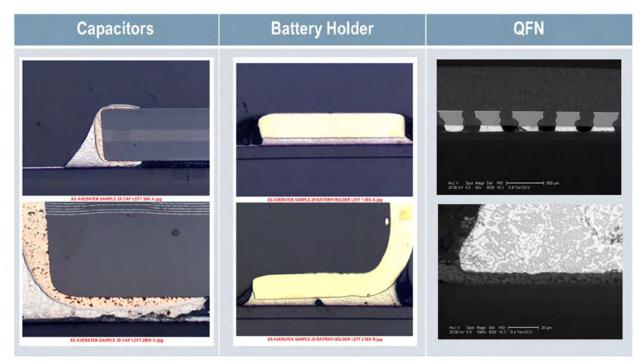

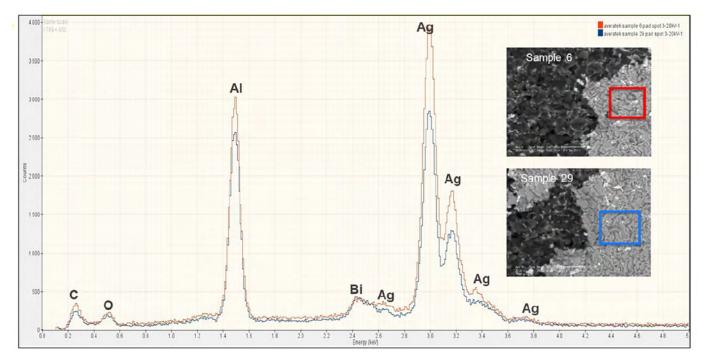

- 76 Surface Treatment Enabling Low-temperature Soldering to Aluminum by Divyakant Kadiwala

- 88 Failures and Reliability in Soldering by Michael Gouldsmith and Zen Lee

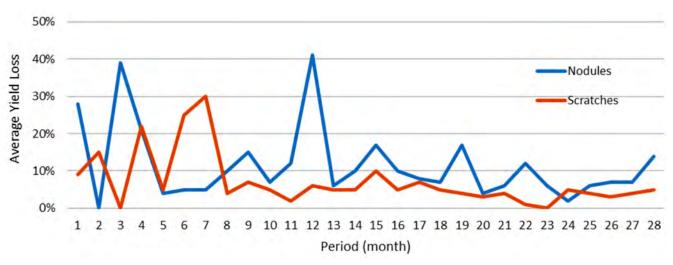

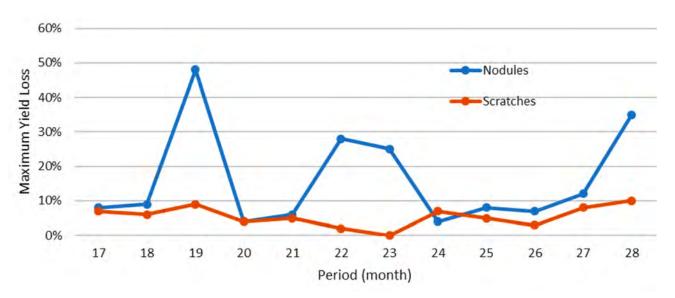

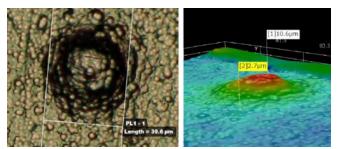

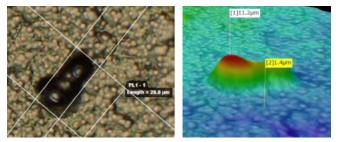

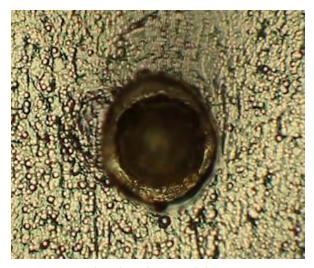

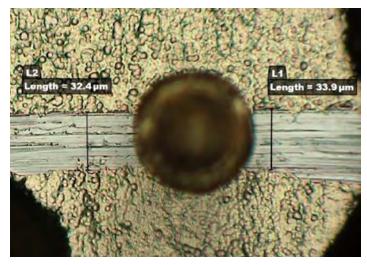

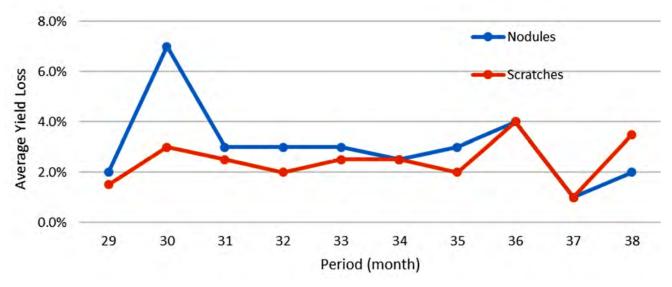

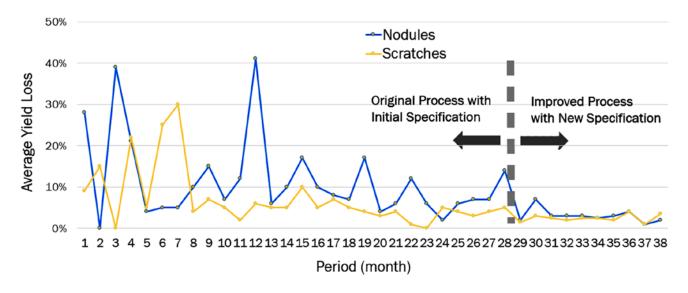

- 96 Approaches to Overcome Nodules and Scratches on Wire-bondable Plating on PCBs by Young K. Song, Vanja Bukva, and Ryan Wong

### FEATURE COLUMNS:

- 28 Would You Prefer Shorts or Opens in Your Products? by Ray Prasad

- 56 The F Word by Eric Camden

- 84 Common Machine Errors and How to Avoid Them by Chris Ellis

### OUR MOST POPULAR EQUIPMENT...IN STOCK

**AP430 Stencil Printer**

Fully-automatic inline printer with automatic vision alignment

RW1500 BGA Rework Removes/Replaces Any SMD **CR-5000 Reflow Oven**

Compact with profiling and performance of larger ovens

High-mix & frequent job changes, 128 feeder slots, 8,000 CPH

Text or Call Chris - East: 215.869.8374 Ed - West: 215.808.6266 sales@manncorp.com

### MC-389 Pick & Place High speed high mix 10,500 CPH with 96 feeder slots, inline configuration

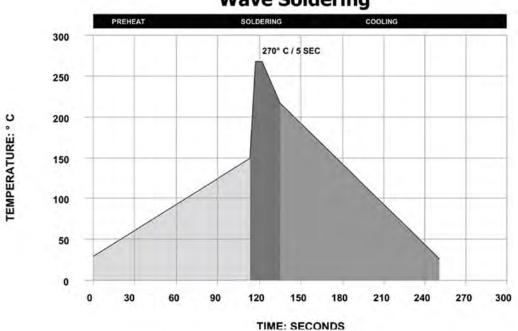

### 16.350 Wave Solder

Preheat pause feature to simulate large machines using less floor space

Huntingdon Valley, PA • San Diego, CA

© 2019 by Manncorp

#### JULY 2019 • ADDITIONAL CONTENT

## SNT007 MAGAZINE

### SHORTS:

- 9 Engineering Heat Transport

- 26 Flexible Generators Turn Movement Into Energy

- 55 Mastering Magnetism

- 59 Goepel electronic Solutions, Webinar Series, and Trends

- 86 Quantum-squeezed Light Cuts Noise

- 120 Octopus-inspired Wearable Sensor

- 125 Scientists Create New Class of Two-dimensional Materials

### **ARTICLE:**

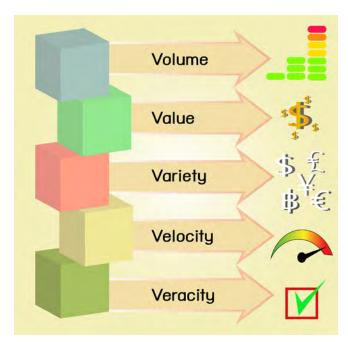

114 Smart Manufacturing Roadmap: Data Flow Considerations for the Electronics Manufacturing Industry by Ranjan Chatterjee and Dan Gamota

#### **COLUMNS:**

8 Reliability vs. Failure by Nolan Johnson

- 10 Learn From the Wise by Dr. Jennie S. Hwang

- 122 BGA and PCB Warpage: What to Do by Bob Wettermann

- 126 Becoming the Preferred Supplier, Phase 2: The Six Pillars by Alfred Macha

### **HIGHLIGHTS**:

- 27 Market

- 75 Supplier

- 87 MilAero007

- **132** Top 10 from SMT007.com

### **DEPARTMENTS**:

- 135 Career Opportunities

- 144 Events Calendar

- 145 Advertiser Index & Masthead

#### 6 SMT007 MAGAZINE I JULY 2019

Since we first began in 1985, delivering the highest quality products possible has been our first priority. Our quality control systems are certified and we renew our commitment to quality each and every day.

Delivering quality products on time, combined with timely and accurate communication from our customer service team is how we create lasting relationships with our customers.

### Take a look at our quality »

### **COMMERCIAL • MILITARY • MEDICAL • BAREBOARD**

U.S. Circuit, Incorporated 2071 Wineridge Place Escondido, CA 92029 +1 (760) 489-1413 www.uscircuit.com

# **Reliability vs. Failure**

#### Nolan's Notes by Nolan Johnson, I-CONNECTO07

Summer is officially underway here in the Northern Hemisphere, and just like the temperatures, we're turning up the heat in this issue and getting technical. Enter "Reliability Man," the hero who must persevere against all the challenges thrown in his path.

It should come as no surprise that solder and solder joints are often at the center of attention in electronics assembly when discussing failures and reliability. Failed components aren't under the direct control of the assembly operation nor is a board failure. But the joining of the two? That's all you, contract manufacturers.

Thankfully, there is a significant amount of ongoing research into the specialty of solder joint reliability. Lead-free initiatives continue to drive this research. Industry watchers might say that we're just now beginning to understand a few of the long-term effects of removing lead from solder. Some space and mil-aero applications continue to specify tin-lead solder only. For these applications, one can argue that environmental

impact is simply not a high-priority concern; their products are not generally destined for the landfill. But long-term reliability in an environment where repair is not an option and safety and survivability are critical is a high-priority concern. But the solder evolution isn't limited to electronics. My neighbor is a plumber. Every Monday, he stops by my house to pick up three dozen eggs-about a day's production when one's residence comes complete with 50 laying hens-so I asked him how he likes leadfree solder for pipefitting. "It works," he said, "but it's a completely different skill set to use lead-free solder. It doesn't behave the same." Readers who work in the assembly industry know exactly what he's talking about.

Don't get me wrong; I'm not anti-RoHS. My point is that there is a great deal of ongoing research into materials, chemistries, thermal profiles, and precise process controls to create that completely different skill set my plumber neighbor had to teach himself. This is a time of great change and innovation for solders and conformal coatings.

As we put this issue together, it became clear that we needed technical papers on the cutting-edge of failure and reliability research. Not everyone dives deeply into the technical papers, but for those of us whose job it is to reliably deliver failure-free products, we should be aware of the latest findings. This issue brings you some of the most insightful technical research from IPC APEX EXPO 2019.

Dr. Jennie Hwang kicks the issue off with a piece titled "Learn From the Wise." And Nihon Superior's Keith Sweatman brings us his work on solder paste volume optimization for low-temperature BGA reflow. Ray Prasad follows with his column, asking, "Would You Prefer Shorts or Opens in Your Products?".

Tony Lentz addresses solder powder size in his paper, "Size Matters: The Effects of Solder Powder Size on Solder Paste Performance." Then, Eric Camden's column discusses "The F Word"—failure. Following right behind is Rusty Osgood, et al., and their paper on "Lowtemperature SMT Solder Evaluation."

Treating the surface of aluminum for low-temperature soldering is the topic of discussion

in Divyakant Kadiwala's paper. Next, Chris Ellis looks at "Common Machine Errors and How to Avoid Them."

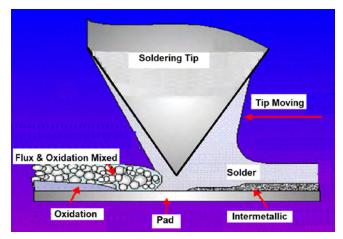

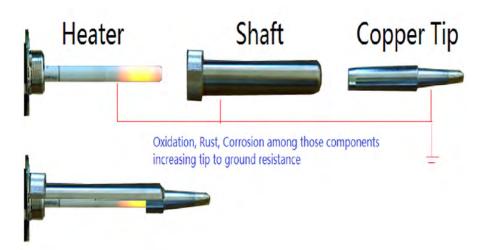

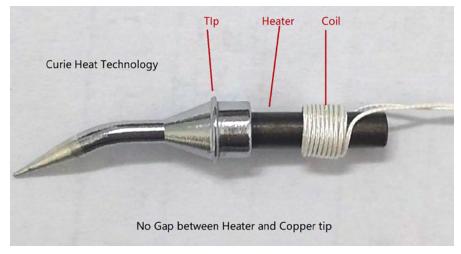

Thermaltronics' Michael Gouldsmith and Zen Lee consider "Failures and Reliability in Soldering" at the tip of the soldering iron. Then, Young Song, et al., share their findings in overcoming nodules and scratches on wire bondable plating.

Ranjan Chatterjee and Dan Gamota bring us the iNEMI Smart Manufacturing Roadmap discussion on "Data Flow Considerations for the Electronics Manufacturing Industry." Then, Bob Wettermann discusses BGA and PCB warpage, and Alfred Macha continues his series on becoming a preferred supplier. This time, he goes into detail on "The Six Pillars."

So, put on your heat-resistant gloves; this issue is going to be as hot as an Arizona parking lot in July. Enjoy! SMT007

Nolan Johnson is managing editor of *SMT007 Magazine*. Nolan brings 30 years of career experience focused almost entirely on electronics design and manufacturing. To contact Johnson, click here.

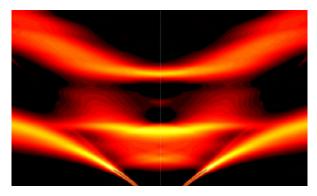

### **Engineering Heat Transport**

Scientists have discovered a way to alter heat transport in thermoelectric materials—a finding that may ultimately improve energy efficiency as the materials convert heat flow into electricity. Caltech theorists simulating the thermoelectric material lead selenide saw something surprising—a thermal wave that did not propagate. They determined the trick to potentially increasing energy effi-

ciency in this material was to stop heat-carrying vibrational waves without thwarting electricity-bearing electrons.

To verify the discovery, they called on experimentalists to probe a real crystal. "Vibrational waves stop propagating in a perfect crys-

tal because of nonlinear interactions between phonons," said Michael Manley of Oak Ridge National Laboratory (ORNL).

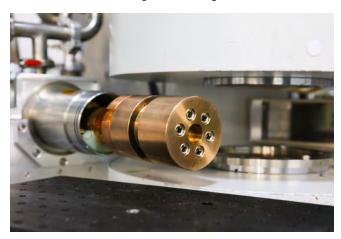

The experiment used neutron scattering at ORNL's Spallation Neutron Source and the National Institute of Standards and Technology's Center for Neutron Research and X-ray Scattering at Argonne National Laboratory's

> Advanced Photon Source. The discovery improves understanding of thermoelectric performance and may enable unconventional heat transport in future materials. The research was published in *Nature Communications*.

> (Source: Oak Ridge National Laboratory)

### Learn From the Wise

### SMT Prospects & Perspectives by Dr. Jennie S. Hwang, CEO, H-TECHNOLOGIES GROUP

How can we get ahead in this digital world inundated with a gargantuan amount of information available to all? More sustainably, how can we stay ahead of the curve? Knowledge and wisdom are the fuel to propel us ahead; learning from the wise is the speedier path to acquire the fuel.

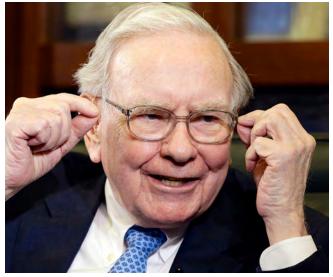

Warren Buffett

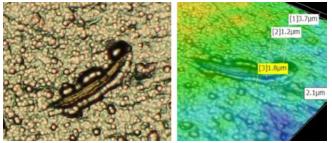

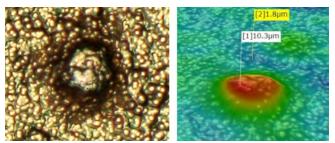

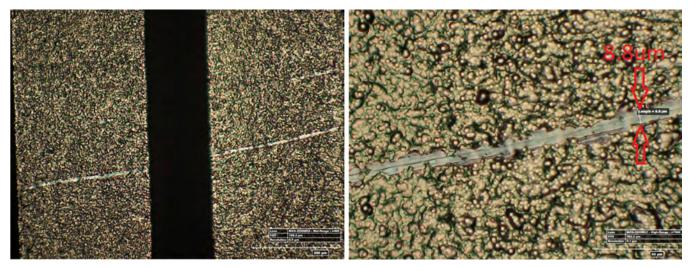

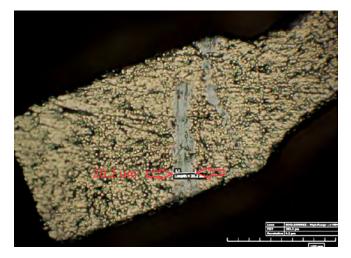

Business magnate Warren Buffett—one of the most successful investors in the world holds a wealth of knowledge and wisdom. I wanted to attend the Berkshire Hathaway annual shareholders meeting regularly, but work schedule commitments persistently trumped my desire to attend regularly over the last 25 years. Nonetheless, I do make a point to read and study his iconic annual letter to shareholders, which I've found to be enlightening and thought-provoking.

Finally, I decided to make in-person attendance a priority in my work, scheduling way in advance. Last month, I had the pleasure to attend the wisdom-rich event. During the two days of the event, I absorbed or gained a bounty of observations, new ideas, renewed points, and verified thinking paths. I felt intellectually enhanced and reassured.

There were reportedly more than 40,000 inperson attendees from all over the world and millions watching the livestream of the event remotely. The cross-section of attendees is as wide as can be, from a nine-year-old to senior citizens, spanning all walks of life.

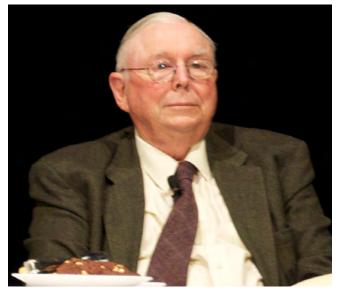

What has attracted so many people? Why are there so many fans and admirers of Buffett and his business partner Charles Munger? Perhaps the simple (overly simplistic) answer is the search for "wisdom" in investments. But more importantly, it is the wisdom above and beyond investment for how to live a long, wholesome, successful life.

Both the Oracle of Omaha, 88-year-old Warren Buffet, and his six-decade-plus business partner, 95-year-old Charlie Munger, devoted almost an entire day to addressing a variety of questions. They shared their wisdom during this meeting and covered topics ranging

Charles "Charlie" Munger

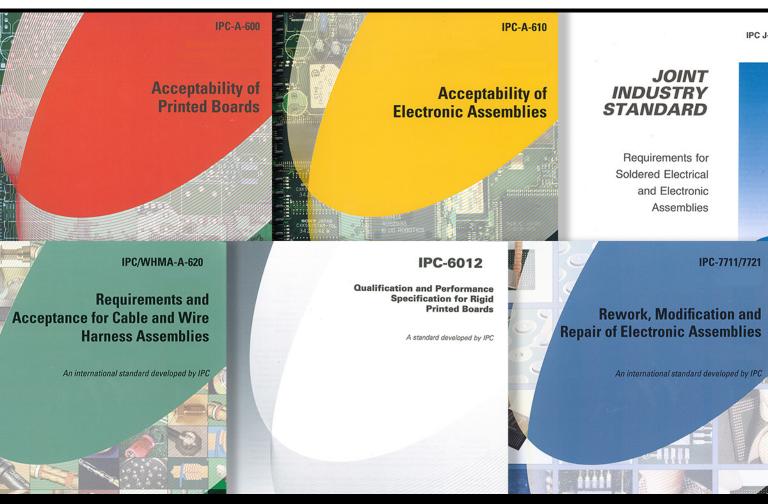

### Now offering new IPC Certification Level: CSE in all six IPC Standards!

The IPC Certified Standards Expert (CSE) certification level was designed for high-level experts in an IPC standard that do not teach or train other people. We're proud to be one of the only centers in North America to offer them!

www.blackfox.com | Phone: (888) 837-9959 | sharonm@blackfox.com

from corporate governance and shareholder relations to human behavior and life lessons, acquisitions, and stock buyback. This wider interest than investment vividly manifested through a variety of questions and discussions, making the event even more intriguing and enriching.

This shareholders meeting is profoundly unique by any measure and in a way that is absent at many corporations, organizations, and institutions around the world. My attendance in-person this time provided me a distinctively deeper appreciation of alternative perspectives in a variety of areas.

Among many intriguing and striking observations, I want to share with our industry a select few that tugged at my heartstrings:

- The attendance of pre-teen kids (ages 9–13) brought by their parents was striking

- A 10-year-old girl asked, "What is your best personal investment?"

- An 11-year-old boy from China asked, "You said you know human nature and behavior better. How does knowing human nature and behavior help investment?"

- A 9-year old girl attending for the third time asked about investing in leading technologies was humored by Buffett, saying, "You should be rich now."

- A 13-year-old boy asked Buffett's thoughts on delayed gratification. Buffett's response was quite educational: "Saving is a necessary thing to do in life, the delayed gratification may not be a qualifier for all individuals or families in all circumstances, but I spend only 2–3 cents on every dollar."

- A 27-year old asked, "I'm young and have a lot to learn. I want to be a successful investment manager. How and when will I know I am ready to successfully manage other people's money?"

- A young woman literally kangarooed with a baby as a first-time attendee who won the "lottery" to ask a question

- Foreign country college students arrived at 3:00 a.m. on the meeting day

- When Mr. Buffett was asked: "What do you value the life most?" he responded, "Time, and I have been able to control my time, and a job that is not limited by physical abilities."

- Mr. Munger was asked, "You have worked with Buffett for more than six decades. Why is he much richer than you?" He answered with his signature touch of humor, "For a lot of reasons. Maybe he is smarter or works harder, but Albert Einstein was not rich."

- Mr. Munger said, "No idea is good enough at any price," which is a superb business acumen

- Mr. Buffett stated, "We always carefully measure ourselves on what we do." Discipline is the key!

- Mr. Munger said, "Warren is a learning machine. He reads a lot"; Buffett added, "Charlie reads more books in a week than I do in a month." This truly coincides with the following famed Buffett quotes, which I couldn't appreciate or agree with more!

- "I think you should read everything you can. In my case, by the age of 10, I'd read every book in the Omaha public library about investing, some twice. You need to fill your mind with various competing thoughts and decide which make sense."

- "Read 500 pages every day. That's how knowledge works. It builds up like compound interest."

On investments, corporate governance, financials, and capital allocation, I felt a deeper sense for the concepts used in measuring a company's performance by operating earnings rather than EBITDA. Mr. Buffett has been championing this approach for some time. I equally understood better the rationale behind the Buffett's stock buyback. I can also see more clearly why Mr. Buffett prefers equity investment to bonds. Not surprisingly, on Buffett's experience in corporate governance, to paraphrase his remarks, " I have served on more than 25 corporate boards. So-called independent directors are not independent at all." How true! Other learning advice is well reflected by an interview by the *Wall Street Journal* from May of this year, Munger stated, "Part of the reason I've been a little more successful than most people is I'm good at destroying my own best-loved ideas. I knew early in life that would be a useful knack, and I have honed it all these years, so I'm pleased when I can destroy an idea that I have worked very hard on over a long period of time. And most people aren't." How pragmatic! Indeed, objectivity is the engine for building up one's wisdom.

Overall, my takeaway thoughts go to the following inferred and inducted points:

- 1. The Buffett/Munger duo create an intellectual synergy. What a fortunate partnership. Good partnership is power!

- 2. There are profound reasons for the overwhelming reverence and admiration for the two

- 3. Pre-teen attendance points to the next generation's high aspiration

- 4. Pre-teen grasp of high-level knowledge demonstrates ever-increasing competitiveness in future generations

- 5. Learning from the wise is a speedier way to get ahead

- 6. Mr. Munger's advice, "No idea is good enough at any price," speaks volumes for astute business decision-making

- 7. A company's healthy and sustainable performance correlates so well with level-headed leadership, including the board and management. This applies to any organization.

- 8. Further appreciation of Buffet's iconic concepts and practices:

- "The best investment you can make is an investment in yourself. The more you learn, the more you'll earn."

- "We don't have to be smarter than the rest. We have to be more disciplined than the rest."

- "If you want to soar like an eagle in life, you can't be flocking with the turkeys."

- "Always associate yourself with people who are better than you."

- "Someone is sitting in the shade today because someone planted a tree a long time ago."

- "Outstanding long-term results are produced primarily by avoiding dumb decisions rather than by making brilliant ones."

- "It's good to learn from your mistakes. It's better to learn from other people's mistakes.

How can we get ahead—and stay ahead of the curve? Speed is the key. Among the fundamental traits, continually and consistently learning from the wise is the speedier path to acquire the fuel to propel us forward. SMT007

**Dr. Jennie S. Hwang**—an international businesswoman and speaker, and business and technology advisor—is a pioneer and long-standing contributor to electronics hardware manufacturing as well as to the environment-

friendly lead-free electronics implementation. Among her many awards and honors, she was inducted to the International Hall of Fame–Women in Technology, elected to the National Academy of Engineering, an R&D-Starsto-Watch, and YWCA Achievement Award. Having held senior executive positions with Lockheed Martin Corp., Sherwin Williams Co., SCM Corp, and CEO of International Electronic Materials Corp., she is currently CEO of H-Technologies Group providing business, technology and manufacturing solutions. She is the Chairman of Assessment Board of DoD Army Research Laboratory, serving on Commerce Department's Export Council, National Materials and Manufacturing Board, Army Science and Technoloav Board, various national panels/committees, international leadership positions, and the board of Fortune-500 NYSE companies and civic and university boards. She is the author of 500+ publications and several books, and a speaker and author on trade, business, education, and social issues. Her formal education includes four academic degrees as well as the Harvard Business School **Executive Program and Columbia University Corporate** Governance Program. For more information, please visit www.JennieHwana.com. To read past columns or contact Hwang, click here.

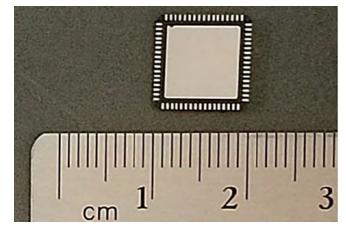

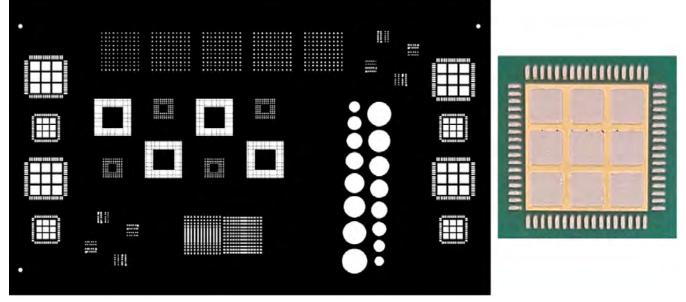

### Optimizing Solder Paste Volume for Low-temperature Reflow of BGA Packages

Feature by Keith Sweatman NIHON SUPERIOR CO. LTD.

### Abstract

The need to minimize thermal damage to components and laminates, reduce warpageinduced defects to BGA packages, and save energy is driving the electronics industry towards lower process temperatures. For soldering processes, the only way that temperatures can be substantially reduced is by using solders with lower melting points. Because of constraints of toxicity, cost, and performance, the number of alloys that can be used for electronics assembly is limited, and the best prospects appear to be those based around the eutectic in the Bi-Sn system, which has a melting point of about 139°C.

Experience so far indicates that such Bi-Sn alloys do not have the mechanical properties and microstructural stability necessary to deliver the reliability required for the mounting of BGA packages. Options for improving mechanical properties with alloying additions that do not also push the process temperature back over 200°C are limited. An alternative

approach that maintains a low process temperature is to form a hybrid joint with a conventional solder ball reflowed with a Bi-Sn alloy paste. During reflow, there is mixing of the ball and paste alloys. But it has been found that to achieve the best reliability, a proportion of the ball alloy has to be retained in the joint, particularly in the part of the joint that is subjected to maximum shear stress in service which is usually the area near component side. The challenge is then to find a reproducible method for controlling the fraction of the joint thickness that remains as the original solder ball alloy.

Empirical evidence indicates that, for a particular combination of ball and paste alloys and reflow temperature, the extent to which the ball alloy is consumed by mixing with the paste alloy depends on the volume of paste deposited on the pad. If this promising method of achieving lower process temperatures is to be implemented in mass production without compromising reliability, it would be necessary to have a method of ensuring the optimum proportion of ball alloy left in the joint after reflow can be consistently maintained.

### Candor Circuit Boards

### Innovative solutions for complex circuit board manufacturing

Click to see what we bring to each sector of the industry:

RF/Microwave PCBs

Automotive Electronics

Power Electronics

Lamination

High-Speed Data

Startups

Our technology produces what our customers dream!

### www.candorind.com | (416) 736-6306

In this article, the author explains how the volume of low-melting-point alloy paste that delivers the optimum proportion of retained ball alloy for a particular reflow temperature can be determined by reference to the phase diagrams of the ball and paste alloys. The example presented is based on the equilibrium phase diagram of the binary Bi-Sn system, but the method could be applied to any combination of ball and paste alloys for which at least a partial phase diagram is available or could be easily determined.

### Introduction

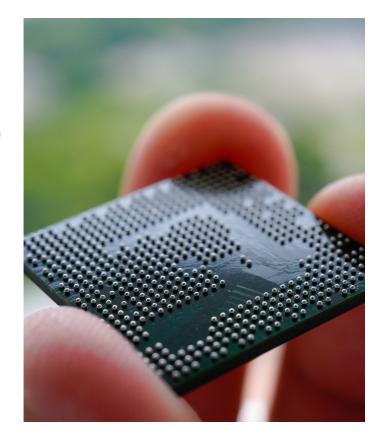

The dependence of the electronics industry on solder to provide the reliable connections necessary to turn a collection of individual components into a functional circuit has created an ongoing dilemma that has challenged the industry since its inception. The main consideration in the design of electronic components is functionality; whether it be to provide a specific resistance, capacitance, or inductance in passive components; logical processing in integrated circuits; and responsiveness in sensors or just electrical connectivity. A need to survive the thermal profile required to form a joint with a molten metal has been an annoying complication.

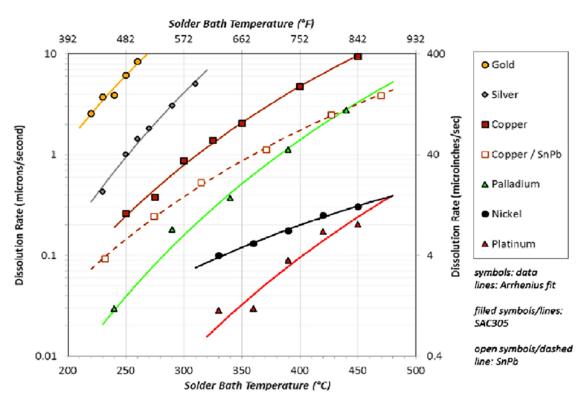

The industry has had a fairly easy start with the Sn-Pb eutectic that has a relatively low melting point of 183°C and mechanical properties and microstructural stability that have been considered to be the benchmark for reliability in service. Because of the need to maximize heat transfer into the joint to get the substrates to wetting temperature, process temperatures (e.g., soldering tool tip temperature, wave solder bath temperature, reflow oven peak temperature) had to be substantially higher than that 183°C melting point. However, with proper process control, the temperature/time profile to which the most sensitive parts of the component were exposed could be kept within a safe limit.

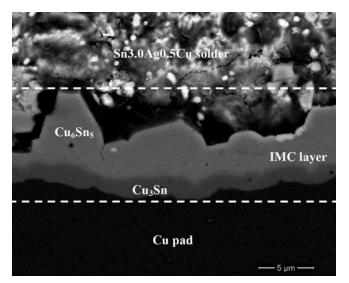

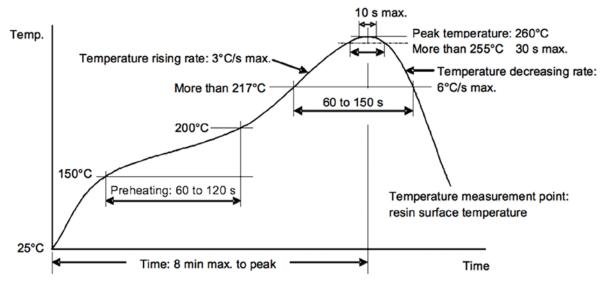

The move to Pb-free solder brought a renewed challenge because the alloy endorsed by IPC as "the Pb-free alloy of choice for the electronics industry"—Sn-3.0Ag-0.5Cu

(SAC305)—does not start to melt until 217°C, which is 34°C higher than the melting point of the Sn-37Pb it was replacing. However, as long as the higher process temperatures could be accommodated by the use of resins and polymers that could survive the higher thermal profiles, the electronics industry was able to adapt to this new alloy.

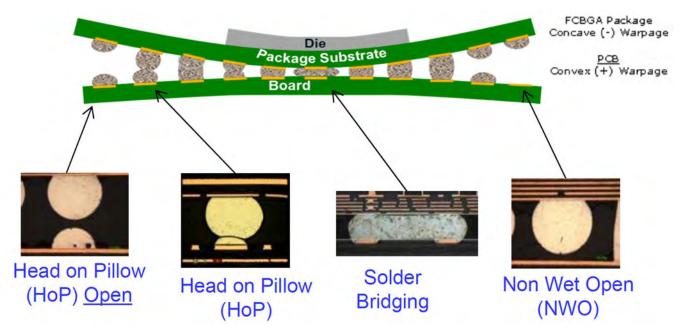

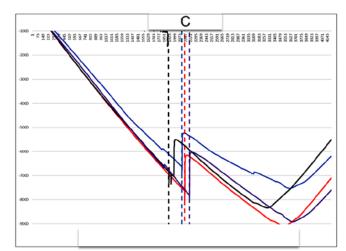

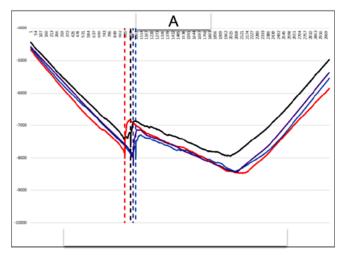

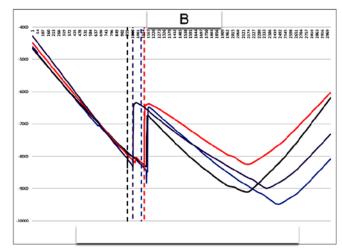

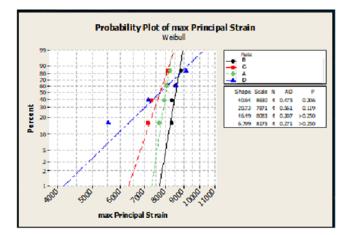

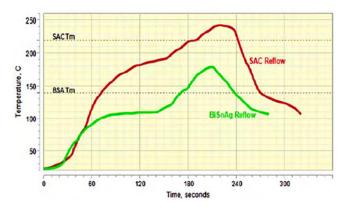

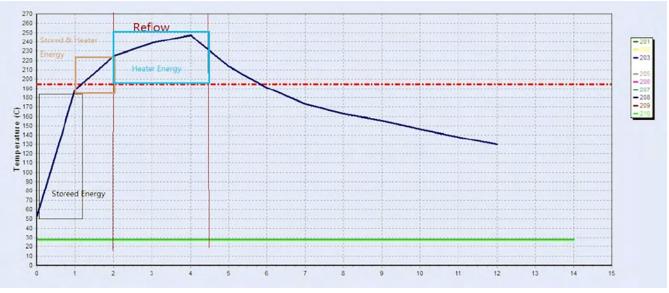

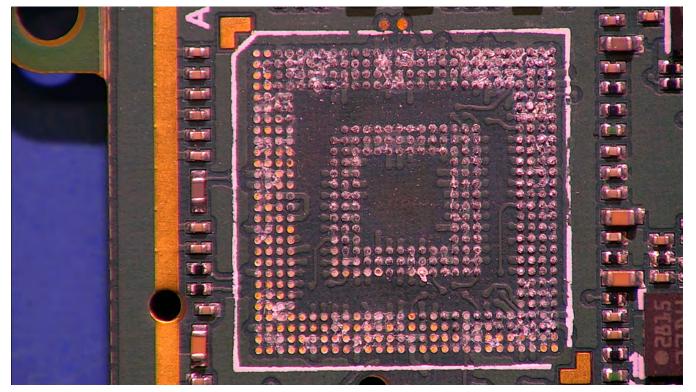

When the problem with higher process temperatures was not just thermal degradation of materials but gross deformation of component packages the challenge moved to a new level. Integrated circuit packages have evolved into complex stacks of a wide range of materials with very different coefficients of thermal expansion so that as the package heats the differential expansion of bonded layers results in warpage of the package. The problem is exacerbated by the temperature gradients that develop within the package as a result of variations in thermal conductivity and thermal mass. The extent of warpage can mean that at its peak the warpage in area array packages is sufficient to cause complete separation of joints at their extreme edges (Figure 1).

Depending on the temperature at which that peak separation is reached for a particular component, the separation can take different forms:

- 1. Unreflowed solder paste can be split with some adhering to the solder ball and some to the pad

- 2. Unreflowed solder paste adheres only to the solder ball and is lifted off the pad

- 3. Unreflowed solder paste adheres only to the pad with the solder ball detaching from the solder paste

Depending on how the warpage changes as a function of temperature, the solder paste might reflow while separation is at its peak. When, later in the reflow profile, the component returns to its original shape, there is no certainty that the separate and now molten solder will coalesce as the activity of the flux, which facilitates wetting and coalescence might have been exhausted. In the case of Type 1 separation, the result is a defect known as head-

Figure 1: Defects caused by dynamic warpage of FCBGA components during reflow soldering <sup>[1]</sup>.

in-pillow (HIP). In the case of Type 2 and 3 separation, the result is a defect known as a non-wet open (NWO).

Because the design of the layers of the package and the selection of materials is determined by many complex considerations that cannot be compromised by a need to minimize warpage at the peak process temperature, ways of reducing process temperature have had to be sought. For many years, the electronics industry has been aware of-and made limited use ofsolders based around the Sn-57Bi eutectic that has a melting point of 139°C. With that melting point, the peak process temperature could be kept below 200°C, at which the component warpage is low enough that the risk of separation defects is significantly reduced. However, this alloy is brittle and cannot deliver the reliability required in joints to area array packages. The reliability of Sn-Bi alloys can be improved by reducing the bismuth content and adding small amounts of elements, such as silver or lead, but the alloy still cannot match the reliability of the higher melting point alloys. And as the composition moves further away from the Sn-Bi eutectic, the liquidus temperature increases, necessitating high process temperature.

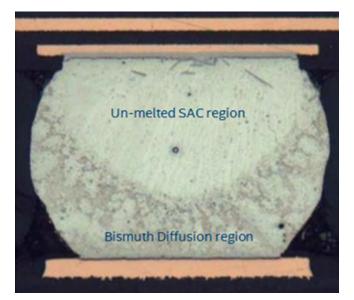

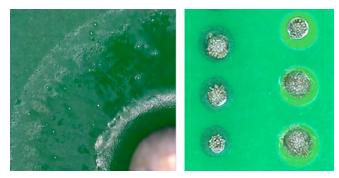

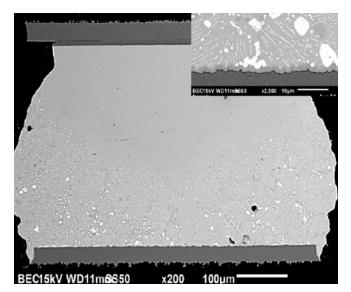

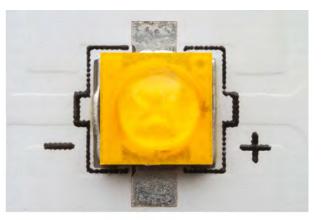

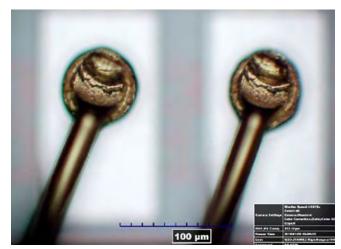

A solution that the industry is now evaluating is to continue to use a conventional SAC alloy for the BGA ball but to reflow solder the package to the substrate with a low-meltingpoint alloy based around the Sn-57Bi eutectic. With this technique, it is possible to securely attach a BGA package to a substrate with a peak process temperature under 200°C. The result of this process is a joint such as that in Figure 2<sup>[2]</sup>.

Reliability testing of these mixed alloy or hybrid joints indicates that as long as a sub-

Figure 2: Typical joint formed by reflow of an Sn-Ag-Cu solder ball with an Sn-Bi low-melting-point solder.

stantial part of the SAC ball alloy remains after the soldering process, the joints have adequate reliability. The distribution of strain in a typical assembly means that it tends to be concentrated in the outer areas of solder close to the interface with the component package. If the solder in that area is an allov that is known to deliver the required service life under the expected conditions, then the reliability of the mixed alloy joint is comparable with that of a joint that is

reflowed with the same alloy as the BGA ball. The challenge with this technique has been determining how to complete the mixed alloy reflow soldering process with sufficient of the original ball alloy remaining on the component that an adequate level of reliability can be achieved.

While there has been much discussion about "Bi diffusion" from the low-melting-point solder into the SAC alloy, the purpose of this article is to explain that the extent to which the BGA ball is lost to the mixed alloy is determined by the thermodynamics of the alloy system made up of the solder ball and the solder paste. Those thermodynamics are neatly summarized in one of the basic tools of the material scientist—the equilibrium phase diagram.

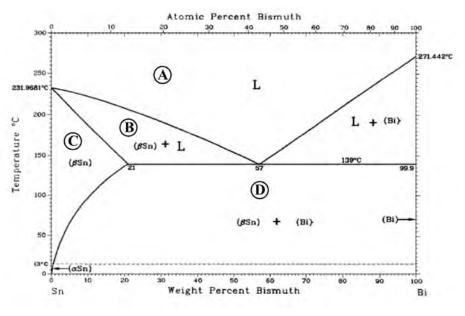

### The Equilibrium Phase Diagram

The equilibrium phase diagram can be considered a map of the location of phases—liquid or solid—in space defined by the dimensions of composition and temperature. Where vapor pressures are significant, a third dimension is pressure. But in the case being considered here, at the process temperatures being used, the alloy constituents have relatively low vapor pressures so that dimension need not be considered.

For a particular composition at a specific temperature, an equilibrium phase diagram

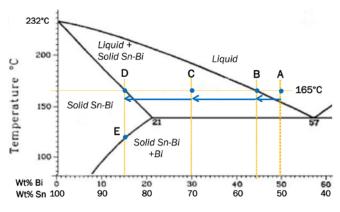

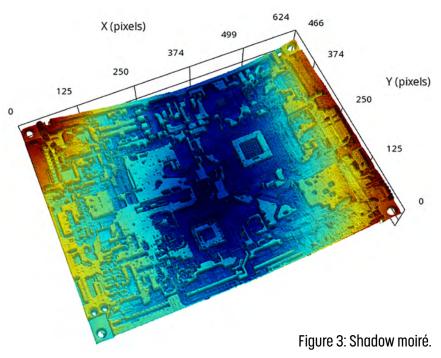

Figure 3: The Sn-Bi equilibrium phase diagram.

will show what phases are present and their composition. With the application of the "lever rule," the relative proportions of the phases present at any such point can be calculated. For a binary system (i.e., in the case of an alloy, a mixture of two metals), the phase diagram is two-dimensional. The phase equilibria for three elements can be presented in a threedimensional diagram, or if the level of one element is fixed, as a two-dimensional pseudobinary plot. For more than three elements the level of one or more of the elements has to be fixed to reduce the number of dimensions to three or two.

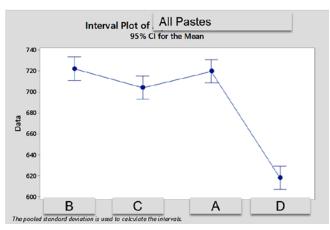

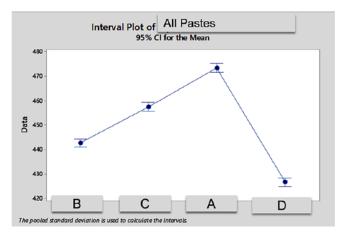

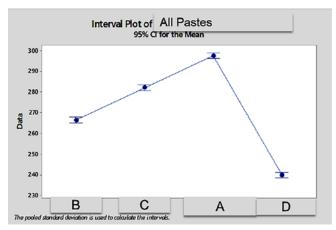

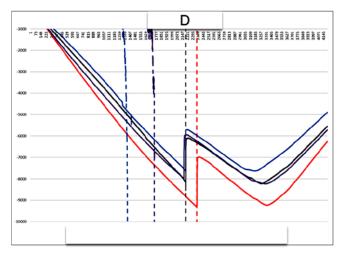

Figure 3 is the equilibrium phase diagram for the binary Sn-Bi system on which the lowmelting-point alloys used in mixed alloy reflow are currently based. An alloy with the composition and temperature at Point A would be entirely liquid. An alloy with the composition and temperature at Point B would be a roughly 50/50 mixture of liquid and solid Sn-Bi alloy with about 10wt% Bi in solid solution. An alloy with the composition and temperature Point C would be completely solid with about 5wt% Bi in solid solution. An alloy at the composition and temperature Point D would be completely solid with a roughly 50/50 mix of nearly pure Bi and Sn with about 15% Bi in solid solution.

0

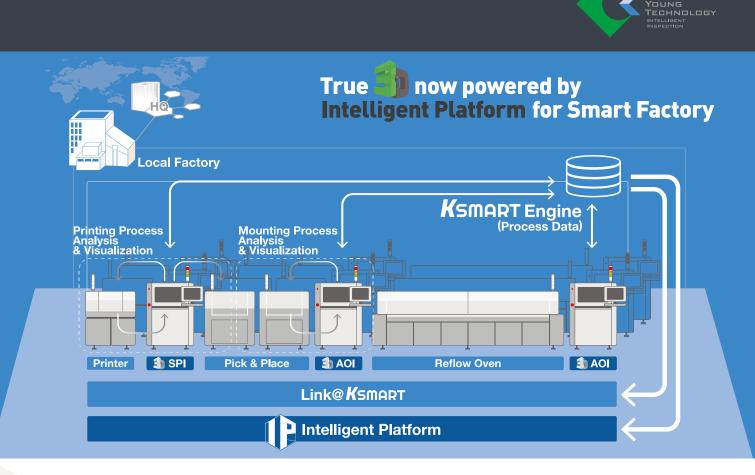

Speed

System

World's No.1 Inspection Company, now powered by Intelligent Platform from Programming to Optimization

#### World's Fastest True 3D AOI

#### Koh Young America, Inc.

6150 W. Chandler Blvd., Suite 39, Chandler, AZ 85226 Tel: +1-480-403-5000, E-mail: america@kohyoung.com

### The Model

A solder ball and the solder in the deposit of solder paste on which it is mounted can be considered as an isolated system in that all the materials that will form the final solder joint are already present. In that regard, it is different from a joint being wave soldered in which there is a virtually unlimited supply of solder on which the joint substrates can draw to form a fillet.

To the extent that during the soldering process, there can be some reaction between the copper or nickel substrates, those substrates should also be considered as part of the system; whether those reactions need to be taken into account depends on the size of the solder ball. In some very small joints, the Sn from the solder and the solder ball consumed in the reaction with the substrates to form the intermetallic compounds Cu<sub>6</sub>Sn<sub>5</sub> or Ni<sub>3</sub>Sn<sub>4</sub> could be a significant fraction of the total amount of Sn available in the solder ball/solder paste system. However, for the purposes of explaining the method of calculating the extent to which the solder ball is consumed in the process of reflow with a low-temperature solder, that effect will be neglected. Where reactions with substrates are significant, they can be factored into the calculations.

For the purpose of explaining the method, the system will be simplified to a solder ball and the solder in the solder paste. In a solder paste, the solder itself accounts for about 50% of the paste volume. The remainder is the flux medium that determines the printing characteristics and tackiness of the paste, provides the fluxing action required to facilitate coalescence of the powder particles into a single mass of solder and the wetting of the joint substrates, and controls the surface tension of the liquid solder that determines the joint profile. However, once the solder ball has been wetted, the flux medium plays no role in the process that determines how much of the BGA ball is lost to the mixed alloy.

To further simplify the explanation of the method, it will be presumed that the solder ball is pure Sn and the low-melting-point solder a simple binary Sn-Bi alloy. For the low-Ag SAC

alloys often preferred for BGA spheres because their greater compliance reduces the incidence of pad cratering in drop impact, the alloy is already about 98.5wt% Sn (with the remainder typically being 1wt% Ag and 0.5wt% Cu). Even SAC305 is 96.5wt% Sn (with the remain-der 3wt% Ag and 0.5wt% Cu).

The process that determines the extent of penetration of the LMP alloy into the ball involves only the Sn. The Ag is present only as the Ag<sub>2</sub>Sn intermetallic compound and the Cu as the intermetallic compound Cu<sub>2</sub>Sn<sub>2</sub> both of which remain in fairly stable equilibrium with the Sn phase over the likely temperature range of the mixed alloy reflow process. Therefore, they would play no role in the interactions that occur in the reflow process. With the likely tolerances on the quantities of the materials in the system, the difference in the outcome with a pure Sn ball should not be very different from that with SAC alloy balls. However, with the basic principle established, allowance can be made for the presence of Ag and Cu in the BGA ball alloy.

Commercial Bi-Sn alloys usually contain a small alloying addition to improve their properties—typically 0.5wt% of Ag or Sb. Over the temperature range of the mixed alloy reflow process, the Ag has no solubility in Bi and would be expected to be present in the low-melting-point solder as the Ag<sub>3</sub>Sn intermetallic compound. Sb is completely soluble in Bi and Sn and could play a role in the determination of the final equilibrium, but its effect would be small and will not be taken into account in the proposed model. Again, allowance could be made for its effect once the basic model is recognized.

If the interaction between the solder ball and solder from the solder paste is allowed to proceed to equilibrium, the factors that ultimately determine the extent to which the solder ball alloy is replaced by mixed alloy are:

- The location of the solidus line on the Sn-rich side of the Sn-Bi phase diagram

- The composition of the low-melting-point alloy

- The peak reflow temperature

If the time that the system is held at reflow temperature is limited, then the system might not reach thermodynamic equilibrium. In that case, another factor determining the extent the solder ball is replaced by the mixed alloy will be the time at reflow temperature.

### **The Process**

The process that occurs during reflow can be described as follows:

- 1. The solder powder in the paste melts and coalesces into a single mass of molten solder

- 2. The molten solder wets the substrate pad and the lower part of the solder ball

- 3. The flux medium—having done its job of facilitating reflow and wetting—is displaced from the solder mass but largely remains as a coating on the molten solder, contributing to heat transfer and protecting the molten solder and the lower part of the solder ball from oxidation

- 4. Sn from the BGA ball starts to dissolve in the molten LMP alloy, increasing the Sn content of the molten solder

- 5. Dissolution of Sn from the solder ball continues until the Sn content of the molten solder moves into the two-phase region of the phase diagram when a solid phase—an Sn-Bi solid solution—starts to freeze out of the melt

- 6. Dissolution of Sn from the BGA ball into the molten solder continues until the composition reaches the solidus composition at the reflow temperature at which point dissolution of Sn stops

- 7. With the system then completely solid, the only mechanism by which further intermixing of the LMP alloy and the BGA ball can continue is by solid-state diffusion; during the time available in a commercial reflow, the profile would be negligible

If at this point the temperature is increased, some of the mixed alloy will melt, and there will be an opportunity for more Sn to dis-

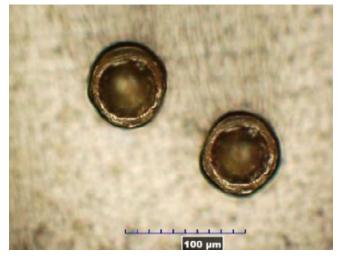

Figure 4: The process of a pure Sn BGA ball dissolving into Sn-50Bi solder at 165°C.

solve from the BGA ball until the composition reaches the solidus at that higher temperature. This process is illustrated schematically in Figure 4 for a low-melting-point alloy that is 50wt% Bi/50wt% Sn and a reflow temperature of 165°C. At the end of Stage 3, the Sn-Bi alloy is fully molten (Figure 4, Point A). If the flux has done its job, the solder will have fully wetted the solder ball as well as the substrate. Sn from the ball would be starting to dissolve in the molten solder, and the Sn content of the molten increases.

At Point B, the Sn content of the molten Sn-Bi alloy has reached saturation (approximately 58wt%Sn). As more Sn dissolves in the remaining liquid, a solid phase starts to freeze out. That phase is a solid solution of Bi in Sn with a composition of approximately 86% Sn. By the time the system reaches Point C (approximately 70wt% Sn), the wt% solid Sn-Bi in the semi-molten solder mix can be calculated by the lever rule as:

$$\frac{BC}{BD} \times 100\% \implies \frac{(42-30)}{(42-14)} \times 100\% \implies \frac{12}{28} \times 100\% \approx 43\%$$

Sn from the solder ball continues to dissolve until it reaches a level of approximately 86wt% (Point D) when the mix of low-melting-point alloy and Sn is completely solid. While the temperature remains no higher than 165°C, the system remains solid with solid-state diffusion the only mechanism as the Bi can migrate further into the solder ball. The only other change in the system predicted by the phase diagram is that as the system cools the mixed alloy phase will cross the solvus line at about 130°C (Point E), which means that the Bi level has reached its saturation limit at that temperature and Bi will start to precipitate out of the Sn-Bi alloy.

### Effect of Bi Level in Low-Melting-Point Alloy

In the example described in the previous section, the length of the line AD provides an indication of the amount of Sn that will dissolve from the ball alloy before the melting point of the Sn-Bi alloy reaches the reflow temperature and the mixing process stops. If the starting alloy were 60% Bi rather than 50%, then more Sn would have to dissolve from the ball alloy before Sn content of the alloy mixture reaches the solvus limit at that temperature. In reality, for a particular reflow temperature, the location of the liquidus line on the Bi-rich side of the eutectic sets an upper limit on the Bi content of the solder that is usable at a particular target reflow temperature.

#### **Effect of Reflow Temperature**

As the temperature increases, the amount of Bi that can be held in solid solution decreases. Put another way, as the Bi content of the alloy increases, when the temperature at which the alloy starts to melt, solidus decreases. In the phase diagram, that trend is reflected in the slope of the solidus line that runs from the melting point of Sn to the limit of Bi solubility in Sn at the eutectic temperature. That means that as the reflow temperature increases, the amount of Sn that will dissolve from the solder ball before the solidus line is crossed and the mixed alloy is completely frozen.

### **Calculating Actual Sn Dissolved**

For a given volume of low-melting-point solder, the amount of Sn that will be dissolved from the solder ball at a particular temperature before the composition of the resulting mixed alloy reaches the solvus can be calculated from the slope of the solidus line.

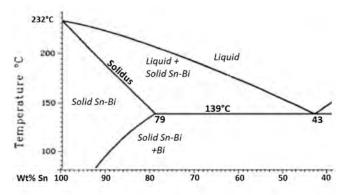

In geometric terms, the solidus line on the Sn-rich side of the Sn-Bi equilibrium phase

diagram in Figure 5 can be described by Equation 1:

#### wt%Sn<sub>s</sub>= 79+( $T_{R}$ -139) x (100-79)

Where  $\% Sn_s$  is the minimum Sn content of the Sn-rich Sn-Bi alloy that is solid at the chosen reflow temperature  $T_R$ . The maximum wt%Sn at the eutectic temperature of 139°C is 79 (Figure 5). When  $T_R$  is set as the melting point of pure Sn (232°C), the equation calculates the wt%Sn at 100% Sn (allowing for rounding errors).

For a given quantity of a low-melting-point Sn-Bi alloy with a chosen Sn content and the chosen reflow temperature, this equation can be used to calculate how much Sn will dissolve from the solder ball before the mixing process is brought to a halt by the composition of the resulting alloy crossing the solidus line. If the objective is that a significant proportion of the original solder ball remains at the completion of the reflow profile, then the volume of solder paste and its initial Sn content would have to be carefully calculated, accounting for the size of the solder ball and the Sn content of its alloy.

### Calculating Paste Volume for Reliable BGA Joints

For the purpose of demonstrating the application of this approach to the design of reliable mixed alloy reflow, the reflow of a 500-µm sol-

Figure 5: Phase diagram used for expressing the slope of the solidus line as a function of Sn content and temperature.

### Whether you are an EMS, CM or OEM, let our bare boards be the foundation you build your reputation upon!

### Technology:

Up to 50 Layers Any Layer HDI Sequential Lamination Blind / Buried Vias Laser Drilling / Routing Heavy Copper

### Materials:

Fr4 Metal Core Isola Rogers Polyimide - Flex Magtron

### We will make only what is needed, when it's needed, and in the amount needed.

You no longer have to worry about long shelf life or tie your capital in bare board inventory.

### -Accultuce inc.

www.PCB4u.com sales@PCB4u.com SAM & ITAR Registered UL E333047 ISO 9001 - 2008

Whether you call yourself an EMS, CM or simply a Bare Board Assembler, Accutrace has you covered.

der ball will be used as an example. A number of other simplifying assumptions are made in constructing this model, but in its practical application to the selection of assembly parameters, actual data would be used.

As in the earlier example, the paste alloy will be a 50wt% Sn Sn-Bi solder. This alloy is slightly hypereutectic with respect to Sn but still has a relatively low liquidus temperature of around 155°C (Figure 4).

Because of the large difference in density between the solder and flux medium, a stencilprintable solder paste is typically about 50% solder by volume. The density of a 50wt% Bi Sn-Bi solder can be estimated by calculation at about 8.4g/cm<sup>3</sup>.

For simplicity, the paste deposit will be assumed to be circular so that the volume of paste is can be calculated as Equation 2:

### <u>πd²</u>x t 4

Where d is the diameter of the paste deposit and t the thickness. With the chosen volume fraction of solder in the paste deposit and the estimated density of the low-melting-point alloy, the weight of solder can be estimated as a function of the thickness and/or diameter of the deposit.

For a reflow temperature of 165°C, the wt% Sn at which the mixed alloy will reach its solidus composition can be calculated by Equation 1 as around 84.5wt%. The amount of Sn required to raise the Sn level in the molten solder can be calculated on the basis of the weight of solder in the paste deposit. It is the dissolution of that Sn that will determine how much of the original solder ball will be lost to the mixed alloy phase in the final joint. A complication is that, in calculating the amount of Sn that will be dissolved from the solder ball to reach the solidus composition at the reflow temperature, allowance has to be made for the diluting effect of the increase in the volume of the molten phase. The calculations made on this basis for a range of paste deposit thicknesses are set out in Table 1.

| Paste Thickness | Paste Volume    | SolderVolume    | Solder Weight | Wt of Sn   | Wt of Sn from Ball | Volume of Sn from Ball |

|-----------------|-----------------|-----------------|---------------|------------|--------------------|------------------------|

| cm              | cm <sup>3</sup> | cm <sup>3</sup> | (g)           | (g)        | (g)                | cm <sup>3</sup>        |

| 0.0010          | 1.9635E-06      | 9.81748E-07     | 8.2467E-06    | 4.1233E-06 | 1.8459E-05         | 0.00003                |

| 0.0020          | 3.92699E-06     | 1.9635E-06      | 1.6493E-05    | 8.2467E-06 | 3.6918E-05         | 0.00005                |

| 0.0030          | 5.89049E-06     | 2.94524E-06     | 2.4740E-05    | 1.2370E-05 | 5.5377E-05         | 0.00008                |

| 0.0040          | 7.85398E-06     | 3.92699E-06     | 3.2987E-05    | 1.6493E-05 | 7.3836E-05         | 0.000010               |

| 0.0050          | 9.81748E-06     | 4.90874E-06     | 4.1233E-05    | 2.0617E-05 | 9.2294E-05         | 0.000013               |

| 0.0060          | 1.1781E-05      | 5.89049E-06     | 4.9480E-05    | 2.4740E-05 | 1.1075E-04         | 0.000015               |

| 0.0070          | 1.37445E-05     | 6.87223E-06     | 5.7727E-05    | 2.8863E-05 | 1.2921E-04         | 0.000018               |

| 0.0080          | 1.5708E-05      | 7.85398E-06     | 6.5973E-05    | 3.2987E-05 | 1.4767E-04         | 0.000020               |

| 0.0090          | 1.76715E-05     | 8.83573E-06     | 7.4220E-05    | 3.7110E-05 | 1.6613E-04         | 0.000023               |

| 0.0100          | 1.9635E-05      | 9.81748E-06     | 8.2467E-05    | 4.1233E-05 | 1.8459E-04         | 0.000025               |

| 0.0110          | 2.15984E-05     | 1.07992E-05     | 9.0713E-05    | 4.5357E-05 | 2.0305E-04         | 0.000028               |

| 0.0120          | 2.35619E-05     | 1.1781E-05      | 9.8960E-05    | 4.9480E-05 | 2.2151E-04         | 0.000030               |

| 0.0130          | 2.55254E-05     | 1.27627E-05     | 1.0721E-04    | 5.3603E-05 | 2.3997E-04         | 0.000033               |

| 0.0140          | 2.74889E-05     | 1.37445E-05     | 1.1545E-04    | 5.7727E-05 | 2.5842E-04         | 0.000035               |

| 0.0150          | 2.94524E-05     | 1.47262E-05     | 1.2370E-04    | 6.1850E-05 | 2.7688E-04         | 0.000038               |

| 0.0160          | 3.14159E-05     | 1.5708E-05      | 1.3195E-04    | 6.5973E-05 | 2.9534E-04         | 0.000040               |

| 0.0170          | 3.33794E-05     | 1.66897E-05     | 1.4019E-04    | 7.0097E-05 | 3.1380E-04         | 0.000043               |

| 0.0180          | 3.53429E-05     | 1.76715E-05     | 1.4844E-04    | 7.4220E-05 | 3.3226E-04         | 0.000046               |

| 0.0190          | 3.73064E-05     | 1.86532E-05     | 1.5669E-04    | 7.8343E-05 | 3.5072E-04         | 0.000048               |

| 0.0200          | 3.92699E-05     | 1.9635E-05      | 1.6493E-04    | 8.2467E-05 | 3.6918E-04         | 0.000051               |

| 0.0210          | 4.12334E-05     | 2.06167E-05     | 1.7318E-04    | 8.6590E-05 | 3.8764E-04         | 0.000053               |

| 0.0220          | 4.31969E-05     | 2.15984E-05     | 1.8143E-04    | 9.0713E-05 | 4.0610E-04         | 0.000056               |

| 0.0230          | 4.51604E-05     | 2.25802E-05     | 1.8967E-04    | 9.4837E-05 | 4.2455E-04         | 0.000058               |

| 0.0240          | 4.71239E-05     | 2.35619E-05     | 1.9792E-04    | 9.8960E-05 | 4.4301E-04         | 0.000061               |

| 0.0250          | 4.90874E-05     | 2.45437E-05     | 2.0617E-04    | 1.0308E-04 | 4.6147E-04         | 0.000063               |

Table 1: Calculation of dissolution of Sn from solder ball as a function of the thickness of the solder paste deposit.

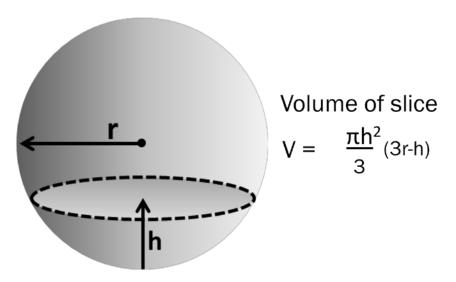

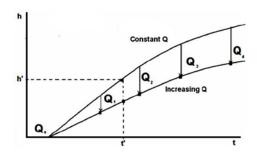

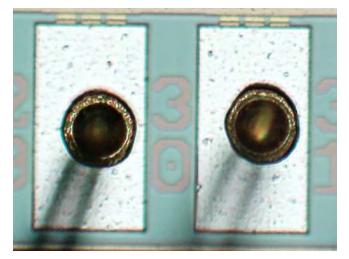

Figure 6: Equation from which the distance h of penetration of the mixed alloy into a solder ball can be estimated.

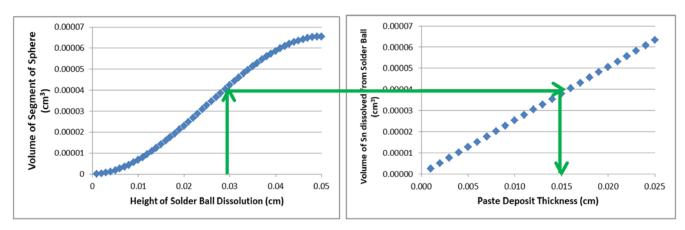

To interpret the volume of Sn that dissolves in the low-melting-point paste in terms of the extent to which the mixed alloy penetrates into the ball, the volume of a slice of a sphere is used as an approximation (Figure 6).

Because of the difficulty of solving the equation in Figure 6 to calculate h when V is known, a graphical solution is used (Figure 7).

In the example illustrated in Figure 7, a 100- $\mu$ m thickness, 500- $\mu$ m print of Sn-50wt%Bi solder paste reflowed at 165°C would result in the formation of a zone of mixed solder that would penetrate about 220  $\mu$ m into a 500-m pure Sn solder ball.

### Conclusions

In practice, as indicated in Figure 2, the interface between the mixed alloy and the remaining solder ball is not planar, but since it is determined by temperature, follow the thermal gradients. However, the point of this exercise is not to make an accurate prediction but to demonstrate the underlying principle that the extent of penetration of the mixed alloy phase into solder can be calculated on the basis of the following:

- The location of the solvus line in the relevant equilibrium phase diagram

- The composition of the low-melting-point solder

- The volume of low-melting-point solder in the solder paste deposit

- The peak reflow temperature

How far the mixed alloy penetrates into the solder ball will depend on the volume of the solder ball.

If a limit is to be set on the amount of original ball alloy that has to be retained to ensure the reliability of the joint than the paste alloy,

Figure 7: The plot on the right is the volume of Sn dissolved in the low-melting-point solder as a function of the thickness of a 500-µm diameter paste deposit, and the plot on the left is the height of a slice of a 500-µm diameter solder ball as a function of the volume of the slice.

the paste volume and the reflow temperature have to be set so that the volume of the ball alloy that will have to dissolve to bring the mixed alloy to its solidus composition at that temperature is no greater than the loss of original alloy volume that can be tolerated. SMT007

#### References

1. S. Mokler, R. Aspandiar, K. Byrd, O. Chen, S. Walwadkar, K.K. Tang, M. Renavikar, & S. Sane, "The Application of Bi-Based Solders for Low-Temperature Reflow to Reduce Cost While Improving SMT Yields in Client Computing Systems," Proceedings of the SMTA International Conference, September 2016.

2. H. Fu, R. Aspandiar, J. Chen, S. Cheng, Q. Chen, R. Coyle, S. Feng, B. Hardin, M. Krmpotich, S. Mokler, J. Radhakrishnan, M. Ribas, B. Sandy-Smith, K.K. Tang, G. Wu, A. Zhang, & W. Zhen, "iNEMI Project on Process Development of BiSn-Based Low-Temperature Solder Pastes–Part II: Characterization of Mixed Alloy BGA Solder Joints," Proceedings of Pan Pacific Microelectronics Conference, 2018.

This paper was first presented at the IPC APEX EXPO 2019 Technical Conference and is published in the 2019 Technical Conference Proceedings.

Keith Sweatman is senior technical advisor at Nihon Superior Co. Ltd. and is an Adjunct Senior Fellow supporting the Nihon Superior Centre for the Manufacture of Electronic Materials at the University of Queensland, Australia.

### **Flexible Generators Turn Movement Into Energy**

Wearable devices that harvest energy from movement are not a new idea, but a material created at Rice University may make them more practical.

The Rice lab of chemist James Tour has adapted laserinduced graphene (LIG) into small, metal-free devices that generate electricity. Like rubbing a balloon on hair, putting LIG composites in contact with other surfaces produces static electricity that can be used to power devices. For that, thank the triboelectric effect, by which materials gather a charge through contact. When they are put together and then pulled apart, surface charges build up that can be channeled toward power generation.

"This could be a way to recharge small devices just by using the excess energy of heel strikes during walking, or swinging arm movements against the torso," Tour said. In experiments, the researchers connected a folded

> strip of LIG to a string of light-emitting diodes and found that tapping the strip produced enough energy to make them flash. A larger piece of LIG embedded within a flip-flop let a wearer generate energy with every step as the graphene composite's repeated contact with skin produced a current to charge a small capacitor.

> "The nanogenerator embedded within a flip-flop was able to store 0.22 millijoules of electrical energy on a capacitor after a 1-kilometer walk," said Rice postdoctoral researcher Michael Stanford, lead author of the paper. "This rate of energy storage is enough to power wearable sensors and electronics with human movement."

(Source: Rice University)

### Electronics Industry News and Market Highlights

### Revenues for NAND Flash Brands 1Q Fall by 23.8% QoQ While Prices Fall Non-stop in 2Q ►

Besides the effects from the traditional offseason first quarter this year, the weakening demand in the fourth quarter of last year has pushed smartphone and server OEMs to begin adjusting their inventories, according to DRA-MeXchange.

### Mobile Services Market in APAC to Increase Focus on B2B and B2B2C Segments ►

The mobile services market in Asia-Pacific (APAC) is expected to focus more on business models for the business-to-business (B2B) or business-to-business-to-consumer (B2B2C) segments as a result of declining revenue from traditional services.

### NB-IoT Device Shipments Reached 53 Million Units in 2018 ►

According to a new research report from IoT analyst firm Berg Insight, global shipments of NB-IoT devices reached 53 million units in 2018, and are expected to almost triple to 142 million units in 2019.

### Global Solar Photovoltaic Services Market 2019-2023 ►

The global solar photovoltaic services market is expected to post a CAGR of more than 16% during the period 2019-2023, according to the latest market research report by Technavio.

### Commercial Aircraft Production to Hit Record High With Renewed Competition Between Airbus and Boeing >

The revival of competition between Boeing and Airbus is expected to result in record delivery of the highly popular narrow-body platforms and a 9.4% year-on-year growth in production.

### Medical Device Contract Manufacturing Market to Reach \$93.1B by 2024 ►

The medical device contract manufacturing market is expected to reach \$91.3 billion by 2024, up from an estimated \$55 billion in 2019 at a CAGR of 10.6% over the forecast period.

### India PC Market Declines YoY for the Third Consecutive Quarter in 1Q19 >

The India traditional personal computing (PC) market declined for the third consecutive quarter in the first quarter of 2019, according to IDC's Asia/Pacific Quarterly Personal Computing Device Tracker.

### EMEA PC Market Will Approach Stability in 2019 >

Shipments of traditional PCs—a combination of desktops, notebooks, and workstations— in the EMEA region will total 71.3 million in 2019, nearly flat year-on-year.

### Global Space Electronics Market Report >

The global space electronics industry analysis highlights that the market generated \$1.27 billion in 2018 and is expected to grow at a CAGR of 5.22% during 2019–2024.

### Smart Manufacturing Platform Market Worth \$10.8 Billion by 2024 ►

The smart manufacturing platform market is projected to grow from \$4.4 billion in 2019 to \$10.8 billion by 2024; it is expected to record a CAGR of 19.7% over the forecast period.

### Would You Prefer Shorts or Opens in Your Products?

#### **SMT Solver**

Feature Column by Ray Prasad, RAY PRASAD CONSULTANCY GROUP

In my last column, I discussed realistic goals to aim for regarding defect levels. I also mentioned, but it is worth repeating, that it may be unrealistic to have zero defect in products right after reflow, but we want zero defect in products we ship to the customer. That is why we spend so much time and money on inspection, test, and repair even though they are nonvalue added process steps, but they are necessary steps since you don't want the customers to discover those defects.

As to the question raised in this column, would I prefer shorts or opens in my products? Neither, thank you. But if I do have to choose, I would choose a more desirable defect, if there is such a thing. But what is a desirable defect? A defect that would never escape inspection and test and would be caught before shipping the product to the customer. Before I answer this question, let me briefly review industry standards on defects and major types of defects that really matter in the functioning of a product.

### Industry Standards and Major Types of Defects

There are three major types of standards in our industry: IPC, EIA, and J-STD. Each one has a different focus, reasoning, and target audience. Having been deeply involved with various standards, chairing many of them over the years, and still chairing many others, let us save this topic for future columns. For now, I will focus on two standards that deal with acceptance criteria for defects.

IPC-610 is a thick and widely purchased IPC standard that specifies acceptance criteria for all types of defects with color photos and very little text. It is easy to read and follow and is primarily targeted at inspectors and operators working on the SMT line.

### DRIVING TECHNOLOGY TO NEW EXCELLENCE

Multilayer, HDI, Bendable, Flex/ Rigid Flex, High Frequency PCBs and more

#### ABOUT CML

CML are the leaders for printed circuit board (PCB) manufacturing and sourcing solutions. CML's mission "We care about reliable connections," apart from the reliable connections of our PCBs, paramount importance is also placed on quality and the relationship between CML, our customers and suppliers.

CML provides a wide product portfolio and a range of services from consultancy, design, engineering, manufacturing and logistics for all markets - convenient and reliable.

CML has a global network, located across 17 international cities and a local presence with a multilingual and culturally diverse team.

### Contact our USA office today

Chris Minard

+1 650 269 4823

### For information on our other offices, please visit our

website: www.cml-globalsolutions.com

CML USA corp. Booth 316 10th September 2019 10am - 6pm

More than a manufacturer

The main standard for acceptance criteria of defects in electronics assemblies is J-STD-001. IPC-610 provides a visual representation of the acceptance requirements established in J-STD-001. This standard (J-STD-001) has very few photos and is full of text and tables targeted at quality and process engineers.

If you go through these standards, there are hundreds of different types of defects. There are week-long classes and certification programs for these standards. However, if you think about it, there are only two types of defects that matter for the functioning of electronic assemblies: shorts or bridges between adjacent leads or opens in solder joints. All of the test methods, such as in-circuit test (ICT) and functional tests only look for shorts and opens because other types of defects can-not be detected by these tests and they don't affect the functionality of the boards. Thus, it goes without saying that we can simplify IPC-610 and J-STD-001, but don't hold your breath.

#### What Defect Should You Aim For?

As I just mentioned, ICT and functional tests can only find opens and shorts; they are not looking for any other types of defects because they cannot find them. If the defects that you see don't fall into open or short category, you can safely classify them as "others." Examples of "others" are insufficient, tombstoning, drawbridge, part movement, etc.

Bridge is the most objective type of defect. No two people will disagree if you show them a bridge. Meanwhile, opens, especially if hidden, can easily escape even ICT and functional tests because they are most likely to make intermittent connections due to pressures exerted during bed of nail testing or ICT.

There is another type of open called insufficient solder joint. Many people will disagree with me calling insufficient joint an open joint, but we all agree that insufficient solder joint is not a total open today but will most likely become an open tomorrow or months later. Therefore, we might as well call it an open. Unlike bridges, insufficient solder joint is the most subjective defect you can find. It is very

| Pitch            | PPM    |

|------------------|--------|

| 16 mils (0.4 mm) | 13,088 |

| 20 mils (0.5 mm) | 18,78  |

| 25 mils          | 950    |

| 50 mils          | 650    |

Table 1: QFP defect levels vs. pitch.

likely that two well-trained inspectors will disagree whether an insufficient solder joint is acceptable or not. To be on the safe side, you might as well consider it an open.

### Industry Findings: Which Defect Is More Prevalent?

In my last column, I quoted a paper by Stig Oresjo<sup>[1]</sup> and Table 1, which shows the level of defects depending on the pitch of a gull-wing device.

Based on Table 1, it is obvious that lower pitches will result in much higher defects because lower pitch devices increase the com-plexity of the manufacturing processes, such as handling, printing, placing, and soldering.

The same paper by Oresjo also analyzed the types of defects for all the components:

- Opens: 46%

- Shorts: 22%

- Insufficient: 17%

As I noted earlier, an insufficient solder joint is an open about to happen in the near future. So, if we combine open and insufficient, almost two-thirds of defects (63%) are opens, 22% are shorts, and the remainder are 15%. This is the average of all types of components in Orse-jo's paper.

The results in the paper on gull-wing devices were even more significant:

- Opens: 65%

- Insufficient: 11%

- Shorts: 16%

- Others: 8%

If you combine opens and insufficient, the number is alarming: 76%. Shorts are only 16% of the total.

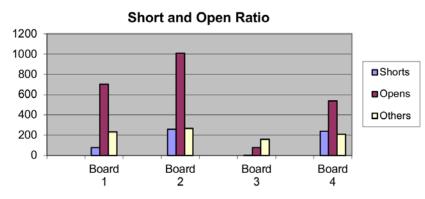

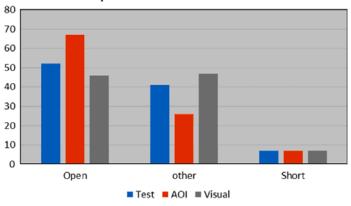

Figure 1: Shorts, opens, and others at a medical company.

#### All products Jan to Oct'2016

### My Findings: Which Defect Is More Prevalent?

This next section details my own findings at two major companies during my consulting assignments—one at a U.S. medical company and the other at a major Japanese electronics company that supplies to the global automotive company (Figures 1 and 2).

### **Recommendations**

An assignment for you is to look at your own data for some of your higher volume products. Put them in three categories: shorts, opens, and others. Put insufficient, tombstoning, drawbridge, part movement, etc., into the open category. For the ones that you cannot put into short or open, call them "others."

I bet that your findings will be no different than what I quoted from Orsejo's paper or my findings. I am sure of it since I have looked at the data at many companies over the years. If I'm wrong, I will buy you a drink (nonalcoholic) if we end up meeting at any industry events, such as SMTAI or IPC APEX EXPO.

My recommendation is to have six to eight times more shorts than opens, but let me be clear that I am not saying have lots of shorts and opens; I am talking about the ratio of shorts to opens. You always want to work

for the total to be on a declining trend, but the total should have more shorts than opens. Why? Shorts will never escape your inspection and test steps, but opens may escape no matter how rigorous your inspection and test regimes are. Opens will be discovered eventually either at a customer site, or even worse, in the field when it is too late and too expensive to fix.

The best part of my recommendation is that it's very easy to achieve. All you need to do to achieve more shorts than opens is to design land patterns and stencils correctly. I may talk about those subjects in future columns. SMT007

#### References

1. Oresjo, S. "Year 1999 Defect Level and Fault Spectrum Study," SMTAI Proceedings, 2000.

**Ray Prasad** is the president of Ray Prasad Consultancy Group and author of the textbook Surface Mount Technology: Principles and Practice. Prasad is also an inductee to the IPC Hall of Fame-the highest

honor in the electronics industry–and has decades of experience in all areas of SMT, including his leadership roles implementing SMT at Boeing and Intel; helping OEM and EMS clients across the globe set up strong, internal, self-sustaining SMT infrastructure; and teaching on-site, in-depth SMT classes. He can be reached at smtsolver@rayprasasd.com. More details at www.rayprasad.com. To read past columns or contact Prasad, click here.

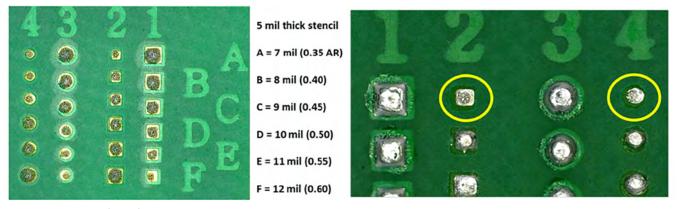

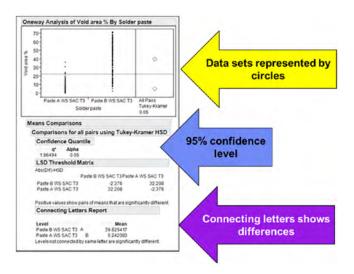

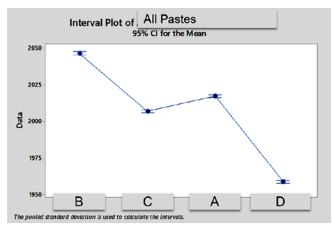

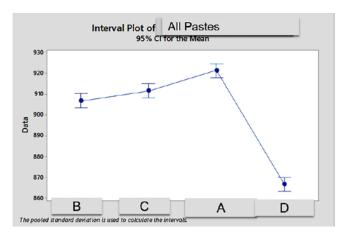

### **Size Size Size Size Size Solder Powder Size** on Solder **Powder Size** on Solder **Paste Performance**

#### Feature by Tony Lentz FCT ASSEMBLY

#### Abstract

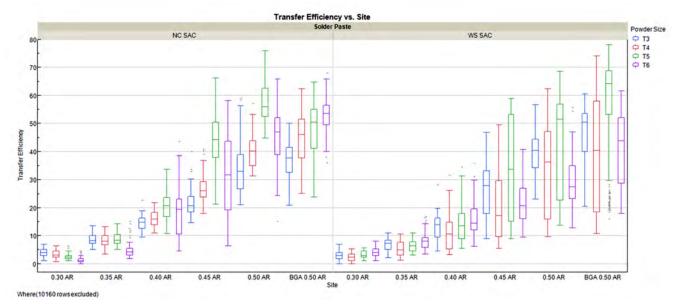

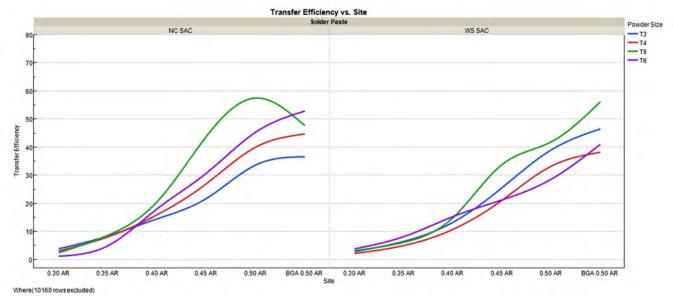

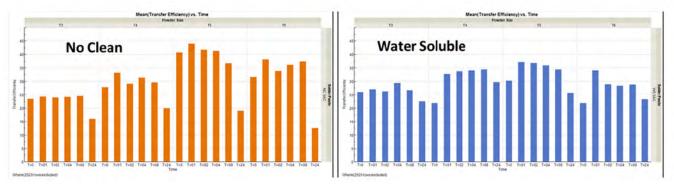

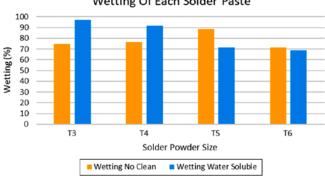

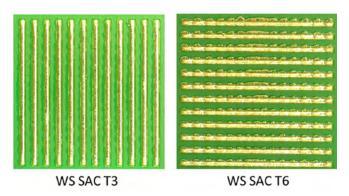

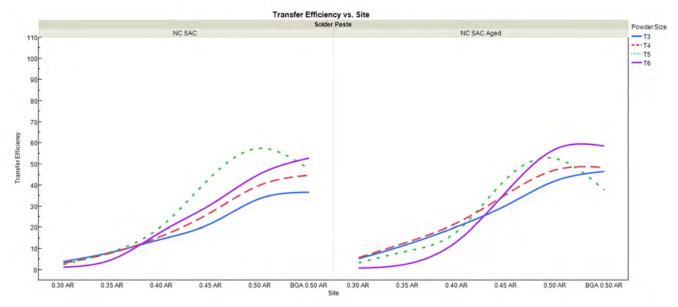

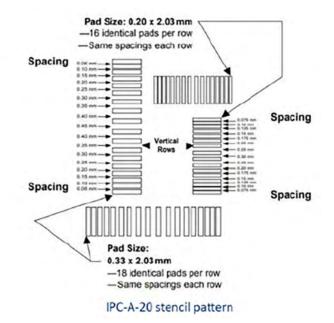

Solder powder size is a popular topic in the electronics industry due to the continuing trend of miniaturization of electronics. The question commonly asked is, "When should we switch from Type 3 to a smaller solder powder?" Solder powder size is usually chosen based on the printing requirements for the solder paste. It is common practice to use IPC Type 4 or 5 solder powders for stencil designs that include area ratios below the recommended IPC limit of 0.66. The effects of solder powder size on the printability of solder paste have been well documented.

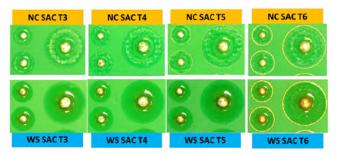

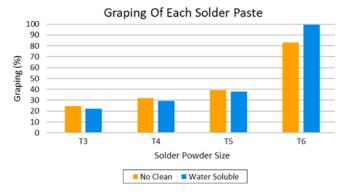

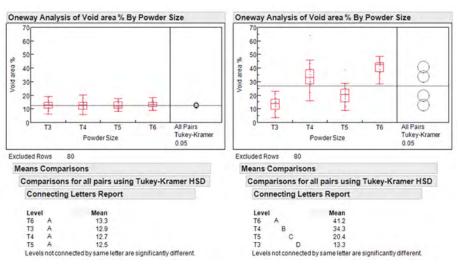

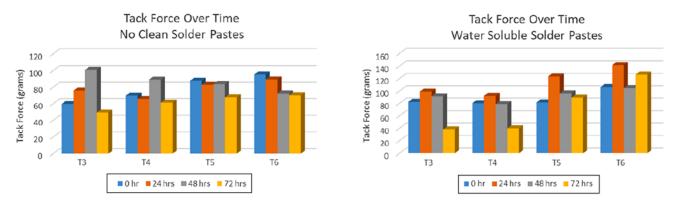

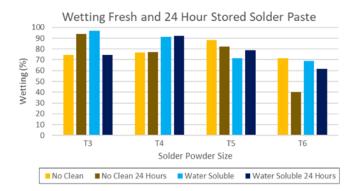

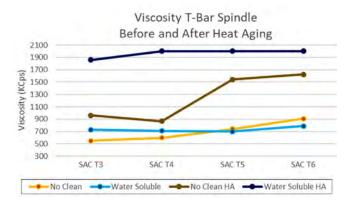

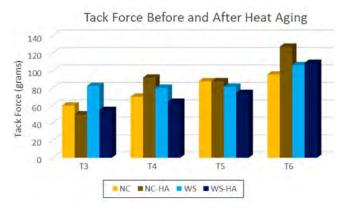

The size of the solder powder affects the performance of the solder paste in other ways. Shelf life, stencil life, reflow performance, voiding behavior, and reactivity/stability are all affected by solder powder size. Testing was conducted to measure each of these solder paste performance attributes for IPC Type 3, 4, 5, and 6 SAC305 solder powders in both watersoluble and no-clean solder pastes. The per-

formance data for each size of solder powder in each solder paste flux was quantified and summarized. Guidance for choosing the optimal size of solder powder is given based on the results of this study.

Keywords: Solder powder size, solder paste performance, solder paste printing, reflow, voiding, solder paste stability

#### Introduction

Size matters. That simple statement is true for many things in life. Small hands are better for speed texting. Large people are better at playing offensive or defensive line in the national football league. Antibodies are micro-

scopically small but they play a key role in our health and wellbeing. Who doesn't want a large cup of coffee (Figure 1)?

Size also matters in the world of solder paste. The size of the solder powder used in a solder paste has

Figure 1: Size matters.

# A BETTER IDEA

### Valor® NPI DFM JUST GOT E A SIER!

Valor NPI software is industry's only automated PCB DFM solution, seamlessly connecting PCB design, fabrication, assembly and test processes.

With the latest version of Valor NPI, setup time for DFM rules can be reduced from weeks to days, and DFM results viewing time can be reduced by up to 50 percent.

LEARN MORE AT HTTP://WWW.MENTOR.COM/NPI

| IPC Type | Less Than 0.5%   | 10% Max.     | 80% Min.     | 10% Max.       |

|----------|------------------|--------------|--------------|----------------|

|          | Larger Than (µm) | Between (µm) | Between (µm) | Less Than (µm) |

| 3        | 60               | 45–60        | 25–45        | 25             |

| 4        | 50               | 38–50        | 20–38        | 20             |

| 5        | 40               | 25–40        | 15–25        | 15             |

| 6        | 25               | 15–25        | 5–15         | 5              |

Table 1: Solder powder size (adapted from Table 3-2 of IPC J-STD-005A).

Figure 2: IPC Type 3, 4, 5, and 6 solder powders.

an effect on solder paste performance. Solder powder sizes are classified by type in the IPC standard J-STD-005 (requirements for soldering pastes) <sup>[1]</sup>. Table 3-2 details the solder powder size ranges for each type, and an excerpt is shown in Table 1.

The main particle size range is normally associated with the type. For example, Type 3 solder powder mainly falls within the 25–45  $\mu$ m size range; therefore, Type 3 solder paste may be labeled as "Type 3 (25–45  $\mu$ m)." Figure 2 shows Type 3, 4, 5, and 6 sizes of solder powder.

Why use Type 4, 5, or 6 solder powder rather than Type 3? The main reason to use smaller solder powders in solder paste is to improve the printability for miniature components. As solder powder size decreases, the solder pastes can be printed through smaller stencil apertures. If the "5-ball" rule is followed from the IPC-7525 stencil design guidelines standard <sup>[2]</sup>, then the minimum aperture size through which printing can occur can be calculated for each solder powder size <sup>[3]</sup>. These calculations for minimum aperture size were performed using five times the maximum solder powder size of the main range (Table 2).

Generally speaking, Type 3 solder paste can be used for components ranging down to the 0402 imperial package size. Most solder paste users prefer Type 4 solder paste for 0201 imperial, micro BGAs, and similar components. Type 5 solder paste is used for even smaller soldering applications like 01005 imperial components <sup>[4]</sup> or when Type 4 solder paste does not print adequately. Type 5 and 6 solder pastes

| IPC Type | Size Range<br>(µm) | Size Range<br>(mil) | Minimum Aperture<br>Size (mil) |

|----------|--------------------|---------------------|--------------------------------|

| Т3       | 25–45              | 1.0–1.8             | 9                              |

| T4       | 20–38              | 0.8–1.5             | 7.5                            |

| T5       | 15–25              | 0.6-1.0             | 5                              |

| Т6       | 5–15               | 0.2–0.6             | 3                              |

Table 2: Solder powder size and minimum stencil aperture size for printing using the 5-ball rule.

are used for dispensing applications, such as jet printing. Type 6 solder paste is also used for other ultra-fine-feature applications <sup>[5 & 6]</sup>.

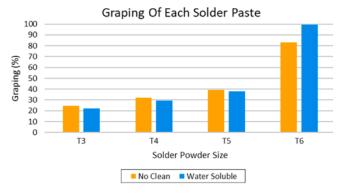

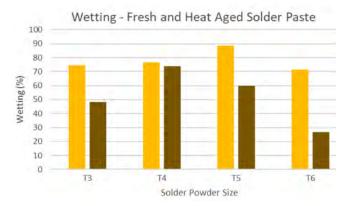

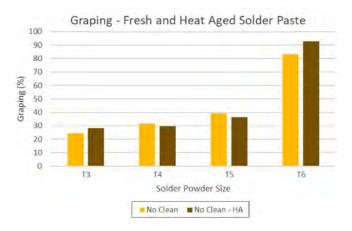

Aside from the printing capabilities given by smaller solder powders <sup>[7]</sup>, other performance changes occur when smaller solder powders are used. Stencil and shelf life of the solder pastes may be shortened when using smaller solder powders. Smaller solder powders have a higher potential for random solder balling and graping. Voiding behavior can also be affected by a change in solder powder size. The goal of this study is to quantify the performance for IPC Type 3, 4, 5, and 6 SAC305 (Sn / Ag 3.0% / Cu 0.5%) solder powders in both water-soluble and no-clean solder pastes. Experimental data for each solder paste is compared and contrasted, and recommendations for the optimal use of each solder paste are given.

### **Methodology**

#### Surface Area of Solder Powder and Reactivity

As the solder powder size decreases, the surface area of solder powder increases for a given mass (Table 3) <sup>[8]</sup>. These surface areas were calculated using the middle value in the main particle size range.

The surface area of the solder powder is important because it plays a role in the reactivity of the solder powder. As the surface area increases, the rate of reaction increases. Imagine trying to dissolve a cube of sugar in a cup of water. It takes time and a lot of stirring for the sugar to dissolve completely. If the same mass of granular sugar is mixed into a cup of water, it dissolves much more quickly (Figure 3).

| ІРС Туре | Middle Surface<br>Area of 1 Kg (m <sup>2</sup> ) |      | Amount of Surface<br>Area Over T3 (%) |

|----------|--------------------------------------------------|------|---------------------------------------|

| Т3       | 22.9                                             | 1.00 | —                                     |

| T4       | 27.7                                             | 1.21 | 21                                    |

| T5       | 40.2                                             | 1.75 | 75                                    |

| Т6       | 80.3                                             | 3.50 | 350                                   |

| Table 3: Solder powder size and |

|---------------------------------|

| surface area for a 1 Kg mass.   |

After one minute of mixing, the granulated sugar dissolved completely while the cube of sugar was partially dissolved. The granulated sugar has a higher surface area than the cube of sugar, which enables the granulated sugar to dissolve more quickly.

The same principle is true with solder powder. The higher surface area of smaller solder powder types causes the rate of reaction to be higher than the larger solder powder types. Therefore, smaller solder powder types are more susceptible to oxidation when exposed to air <sup>[9]</sup>. The chemical reactions for oxidation of tin (Sn) are as follows:

$$Sn_{(s)} + \frac{1}{2}O_{2(g)} = SnO_{(s)}$$

$Sn_{(s)} + O_{2(g)} = SnO_{2(s)}$

As oxygen reacts with the solder powder, metal oxides are created. The primary oxide that forms on SAC305 alloy is SnO <sup>[10]</sup>. The solder paste flux removes the metal oxides and helps to slow further oxidation <sup>[8]</sup>. Oxidation of the solder powder can continue, albeit slowly, as long as the solder paste is exposed to air. Mixing and increased temperature accelerate this process. This reaction process

Figure 3: Granular sugar (L) versus cubed sugar (R) dissolved in water with a 1-minute mix time.

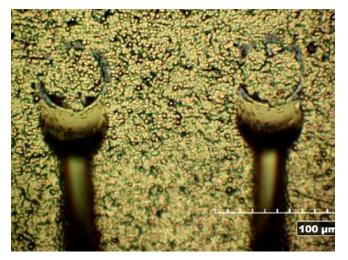

Figure 4: Random solder balling (L) and graping (R).

of solder powder oxidation and oxide removal by the flux tends to thicken the solder paste. Over time, this can lead to clogged stencil apertures and cause the solder paste to stick to the squeegee blades. The usable stencil life of the solder paste may be shortened by the smaller solder powders. The good news is that solder paste fluxes are made with ingredients to protect the solder powder, which significantly slows this oxidation process.

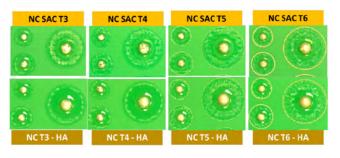

Oxidation of the solder powder also occurs during reflow. The solder paste flux reacts with and removes the oxides from the solder powder during reflow. As the solder powder size decreases, more flux is required to deal with these oxides. When reflowing solder pastes made with smaller solder powder sizes, the flux may run out of activity; then, oxides are left on the solder powder which interferes with the proper coalescence of the solder. Solder pastes made with smaller solder powders are susceptible to potential issues like random solder balling and graping (Figure 4).

The shelf life for solder pastes made with smaller solder powders may also be shorter than solder pastes made with larger solder powders. During storage, the flux can react with the solder metal, creating metal salts. The flux activity is depleted through this reaction over time, and this reaction is faster for smaller solder powder sizes. As more reactive solder pastes age, the solder paste may thicken and a change from a smooth and creamy appearance to more of a dull grainy appearance (Figure 5).

Print and reflow characteristics may degrade over time if the solder paste is too reactive. Solder pastes are formulated to prevent or slow this process. Storing the solder paste in a

Figure 5: Fresh solder paste (L) versus aged solder paste (R).

Figure 6: Print and reflow test circuit board.

refrigerator also helps to slow this process and preserve the intended performance characteristics. Proper storage is especially important to prolong the shelf life of solder pastes made with smaller solder powder sizes.

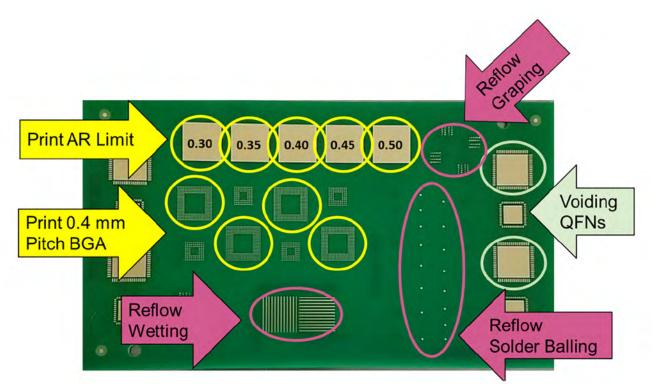

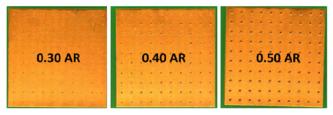

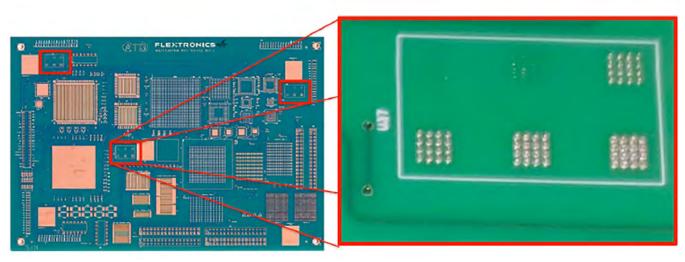

### **Materials and Test Methods**

The circuit board used for this experimentation is shown in Figure 1. This circuit board is made of FR-4 and is 0.062 inches thick with etched copper pads and electroless nickel immersion gold (ENIG) surface finish.

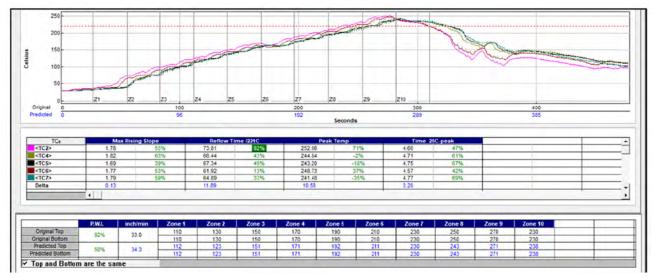

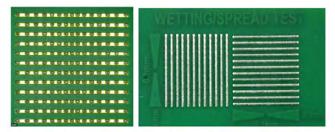

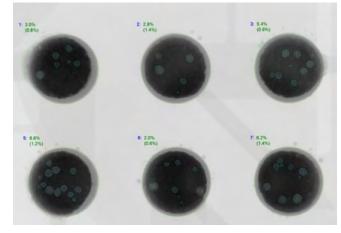

This print and reflow test board has patterns used to quantify printed solder paste volume, wetting or spread, random solder balling, graping, and voiding (Figure 7).

#### **Solder Pastes**

Eight solder pastes were made for this study, including four water-soluble solder pastes and four no-clean solder pastes. The no-clean flux has an IPC J-STD-004 classification of ROL0, and the water-soluble flux is classified as ORH1. The solder alloy chosen was SAC305 (Sn/Ag 3.0%/Cu 0.5%). The solder paste metal concentrations were varied based on solder powder size (Table 4).

Figure 7: PR test board patterns for quantifying print, reflow, and voiding performance.